# ロードマップ全体の技術指標(ORTC)

# 背景

ロードマップ全体の技術指標(ORTC: Overall Roadmap Technology Characteristics の表は、国際技術ワーキンググループ(ITWG)が詳細に章を執筆する活動のための叩き台として、ロードマップ作成過程の初期に利用される。これらの表は、ロードマップ更新作業を行うに当たって特定表間の不整合を強調し、技術ワーキンググループ(TWG)間での整合をとる手段としても使用される。表を改訂するプロセスでは、基本となる傾向モデルを開発して目標値の同意を得るために、ITWG や各 TWG 間で様々なレベルでの調整およびコンセンサス(合意)形成を行なう。この結果、ORTC表は数回の反復と審査の過程を経ることになる。

ORTC 表にはメートル標記の数値が記載され、ロードマップ全体を通して各ワーキンググループの章にはさらに詳しく記載されている。本節に記載される情報は、現在の半導体技術進歩の急速な進展を強調することを目的としている。この情報は 2002 年に開始した改訂と更新作業の集大成となっている。なお ORTC 用語集が付録として載せられている。

# 2003年改訂の概要

# 定義

上で述べたとおり、ロードマップ全体の技術的特長の表に主要技術数値が要約されている。個別の行項目の数値によっては、表の年ヘッダが、集積回路(IC)の開発及びライフサイクル内の異なる点を示すことがあることに注意して頂きたい。しかし、特定の行項目について特に指定しない限り、デフォルトの年ヘッダでは、以前のロードマップと同じく製造サイトからの「生産ツール」を使った製品出荷量が、1万ユニット/月・ICを最初に越えた年を示している。更に 3ヶ月以内に 2番目の会社が生産を開始することが必要である。ASIC (Application Specific IC:特定用途向け集積回路)では、この定義を満たすため、設備で処理した多数の個別製品系列項目の累積量を用いても良い。

一般プレス・リリース発表との混乱を避けるために、特にロジック・テクノロジ・ノードに関して、今年 ITRS の国際ロードマップ諮問委員会(IRC)より、テクノロジー・ノード呼称"hpXX"を表のヘッダーに加えて、明確に区別することになった。この呼称は半導体産業における最も挑戦的な配線ハーフ・ピッチを表しており、現在の所 DRAM セルのメタル・ハーフ・ピッチである。将来のある時点では、違った製品のハーフ・ピッチで表されることもありうる。「テクノロジ・ノード」及び「量産」時期定義の詳細については用語集を参照されたい。

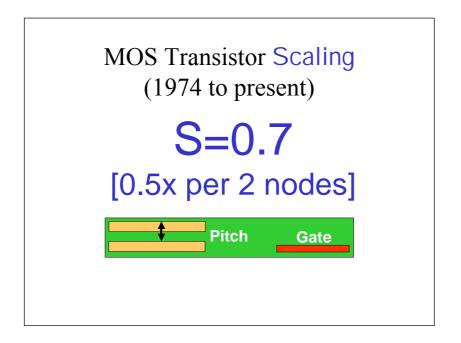

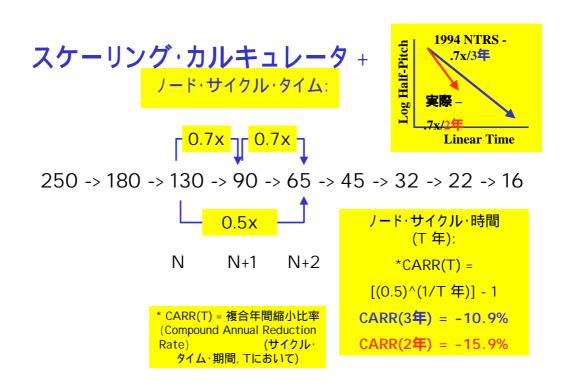

以前確立された IRC ガイドラインと同じに、2003 版ITRSはテクロノジ・ノードの定義をプロセス技術における重要な進歩の達成としている。明確に言えば、テクロノジ・ノードは、ノードあたり約  $0.7\times(2$  つのノードあたり略  $0.5\times)$ 縮小の達成であると定義されている(図 5)。新しいノードに到達するまでの期間は、「テクロノジ・ノードのサイクル」と呼ばれている(図 6)。テクロノジ・ノード間では改善が継続的に行われているが、これは、「短期」テーブル各年欄のノード間データにより反映されている。「長期」テーブルの段は、2003ITRS 年次枠では 2009 年から3年ごとの値(2012、2015、2018)となっているが、以前のITRS 2001 の欄(2010,2013,2016)を参照用として含めている。

図 5 MOS トランジスタ・スケーリング—1974 年 ~ 現在

(注) NTRS (National Technology Roadmap for Semiconductors: 米国内半導体技術ロードマップ)

図 6 スケーリング・カルキュレータ

# ロードマップのタイムライン

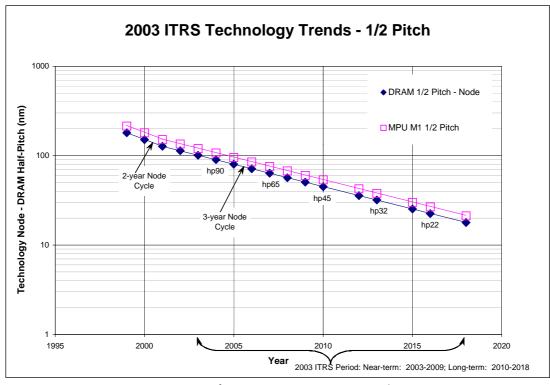

2003 年版ロードマップは、2003 年を基準年として 2018 年までの 15 年間の予測を表している。将来テクロノジ・ノードのタイミング(ノード間 3 年)は 2001 年版と変わっていない。従って、国際的なコンセンサスにより、90nmDRAM ハーフ・ピッチノードの量産立ち上げは、2003 版ITRS「量産」の定義で明確に要求している顧客による製品認可の完了時期によるが、04 年第一四半期から 04 年第四四半期の間に始まるだろう。

2001 版ITRSでは、130 nm ノードは 1 年前倒しされ(1999 版ITRSの 2002 年から 2001 年へ)、350 nm/1995 年以来の傾向であるテクロノジ・ノードの 2 年サイクルを継続している(1997 年 250 nm ノード、1999 年 180 nm ノード)ように思われた。2003 の DRAM製造業者からの、厳しい顧客製品認定に基づく量産立ち上げデータによれば実際の量産立ち上げ時期は次のようであった:350nm/1995、250nm/1998、180nm/2000、130nm/2002。この新しいデータは 2 年のノード・サイクルを示しているが、元の 2001 版ITRSより 1 年遅れている。2003 年に量産立ち上げが行なわれた実際の DRAMのデータで、2003 年ノード間製品が 2001 版ITRSの 100nm か 2003 版ITRSの 110nm で確認されるだろう。130nm/2002 年で 90nm/2004年の 2 年サイクルの可能性もある。この新しい遅れた 2 年ノードサイクルの傾向が続く可能性もあるが、現在の合意は図 7 に示されるように 2003-2018 年のロードマップ期間を通じて DRAM の配線ハーフピッチ・ノードは三年サイクルになると予想している。

上に述べたように、テクノロジ・ノードの達成を定義する上で、DRAM 配線ハーフピッチが、半導体製造の先端技術を最も良く表す機能として使用され続けるだろう。しかし、将来データ解析によって、遅れていた MPU(Micro-Processor Unit:マイクロプロセッサ・ユニット)と ASIC やフラッシュのメタルやポリシリコンの配線ハーフピッチが、2004年以降 DRAM ハーフピッチに追いつき ITRS のヘッダーノード基準になる可能性もある(図 7)。

# 丸められたトレンド数値

新しい DRAM ハーフピッチ・データの入力の結果と 180nm ノードをトレンドの計算起点としているため、2003 年版 ITRS には、テクノロジ・ノードのラベルについて、過去の「四捨五入」方式の訂正が含まれている。 実際の数学的な傾向では、2ノードごとに 50%縮小とし、四捨五入で丸められたノード数値は、1995 年の350 nm から始まり、以下の表Cのようになっている。

| YEAR OF<br>PRODUCTION                      | 1995 | 1998 | 2000 | 2002  | 2003 | 2004 | 2006 | 2007 | 2009 | 2010 | 2012 | 2013 | 2015 | 2016 | 2018 |

|--------------------------------------------|------|------|------|-------|------|------|------|------|------|------|------|------|------|------|------|

|                                            |      |      |      |       |      | hp90 |      | hp65 |      | hp45 |      | hp32 |      | hp22 |      |

| Calculated<br>Trend<br>Numbers<br>(nm)     | 360  | 255  | 180  | 127.3 | 101  | 90   | 71.4 | 63.6 | 50.5 | 45   | 35.7 | 31.8 | 25.3 | 22.5 | 17.9 |

| ITRS<br>Rounded<br>Node<br>Numbers<br>(nm) | 350  | 250  | 180  | 130   | 100  | 90   | 70   | 65   | 50   | 45   | 35   | 32   | 25   | 22   | 18   |

表 C 実際のトレンド数値と丸められたノード数値

半導体産業が新ナノ・テクノロジ(サブ 100nm)の二桁テクノロジ・ノードに入ると、新しい「四捨五入」の訂正が非常に重要になることに注意して頂きたい。いくつかの分野では、過去の ITRS との整合性をとって、

### 4 ロードマップ全体の技術指標 (ORTC)

100 nm/2003 から始まるテクノロジ・ノードを引き続き採用している。これにより、現行の 2003 年版ロードマップの数値 hpXX(70 nm/2006; 50 nm/2009; 35nm/2012; 25 nm/2015)よりも 1 年早い時点にマイルストーンが置かれることになる。IR C の合意事項として、長期の計算には両方の数値の組み合わせが入手できる。もとの 2001 年版ITRSの長期の欄(2010/hp45/45nm; 2013/hp32/32nm; 2016/hp22/22nm)が残され、新しい欄(2012/35nm; 2015/25nm; 2018/18nm)が加えられている。

# ORTCへのアップデート

新しい 2003 年晩ITRS ORTCテクノロジ目標項目として、ロジックメタル 1(M1)ハーフピッチが追加された。これは、ORTCの表 1a と 1b に、以前と同じポリシリコンのハーフピッチと伴に加えられており、産業の状況を反映し、2001 年版ITRSのコンタクトが無いポリシリコンよりもむしろコンタクトがあるメタル 1 のハーフピッチを重視している配線TWGのロジックピッチ目標と合致している。

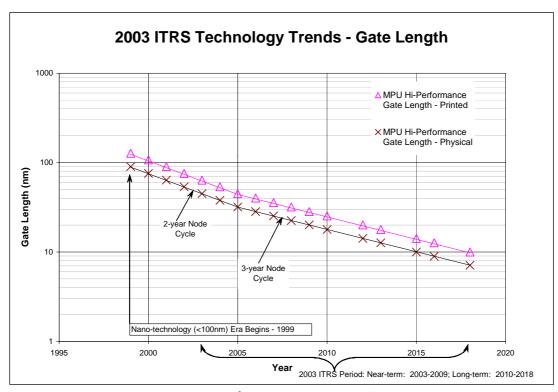

プリントされた MPU ゲート長については、2001 年の積極的とも言える開始点がさらに前倒しとなる大きな訂正が行われた。なお、全プロセスを行ったトランジスタのボトム・ゲート長寸法をさらに縮小することになる新規物理ゲート長は、現在調査確認が行われている。プリント・ゲート長と物理ゲート長の傾向は 2003 年版ITRSでは変更無く、2005 年の MPU の物理ゲート長 32 nmまで、約 70%/2 年サイクルでスケーリングが続くと予測されるが、その後 DRAM ハーフピッチの傾向予測と一致して、3 年サイクル傾向に戻ると期待されている(図8)。

業界のリーダシップを獲得するため、スケジュールを前倒しで達成しなければならない目標のセットとして、ロードマップをガイドする ORTC の技術数値は、半導体関連企業により頻繁に使用されている。このように、激しい競争的環境に置かれている半導体産業では、ORTC の技術数値の大半が、すなわちロードマップそのものが時代遅れになる傾向がある。我々が行う毎年のアップデート・プロセスでは、技術の方向性に関する充分に密着した追跡を国際コンセンサスの場で行うことで、半導体産業における ITRS の有用性を維持することが期待されている。

たとえば、会社の調査データや公の発表と伴に実際のデータや学会の論文を、2 年 / ード・サイクル継続の可能性とともに、2004 年版 ITRSのアップデートで再評価する。加えて、ロジックとフラッシュ製品のハーフピッチの加速を将来のヘッダーの主導権をとる候補として監視する。

上に述べたように、様々なサイクルを反映し、将来のロードマップのシフトを密着して監視するため、2003年~2009年までの期間(「短期」と呼ばれる)の年間技術的要件を作成し、その後、2012年、2015年、2018年と3年(ノード)間隔(「長期」と呼ばれる)技術的要件を作成し、比較が容易なように前の2001年版ITRSの長期の欄を残し三年のサイクルのノードを参照することが出来る方式を継続することが同意されている。

図 7 ITRS ロードマップの加速化は継続—ハーフピッチの傾向

図8 ITRS ロードマップの加速化は継続—ゲート長の傾向

# 製品世代およびチップ寸法モデル

このセクションでは、「製品世代」および製品世代とテクノロジ・ノードとの関係を述べる。というのは、今までこの 2 つの用語を頻繁に区別なく使用してきたからである。しかしながら、3 年ごとに新しい DRAM 製品世代(前世代密度の 4 倍で、基本的に新しい技術機能群に基づく)が誕生するという今までの単純な図式は、テクノロジ・ノードを定義する手段として時代遅れになっている。この 2003 年版 ITRS では、「テクノロジ・ノード」は予測 DRAM 像寸法(最小メタルまたはポリシリコン・ハーフピッチ)とやはリリンクしている。しかしながら、製品の進化/縮小のパスが複雑になるにつれ、このリンクの度合いは減少している。

歴史的にいえば、DRAM 製品は全半導体産業の技術の動輪として認識されてきた。1990 年代初期より前にさかのぼると、ロジック(MPU で代表される)技術は DRAM 技術より遅いペースで開発されていた。しかし、ここ数年の間に、マイクロプロセッサ製造に使用される新規技術の開発速度は加速されている。マイクロプロセッサ製品は、DRAM とのハーフピッチ技術とのギャップを急速に縮めており、現在では特に、プリント・ゲート長と物理ゲート長の孤立ライン機能を処理する能力について、最先端のリソグラフィ装置およびプロセスの開発を推し進めている。2003 年版ロードマップでは、DRAM 製品とマイクロプロセッサ製品が技術リーダシップの役割を共有している。

しかしながら、この 2 つの製品ファミリの間には、いくつかの基本的な差異が存在する。コスト削減および 工場生産性向上への商品市場の経済的な圧力が強いために、DRAM 製品ではチップ寸法の最小化が強 調されている。そのため DRAM の技術開発は、主にメモリ・セル占有面積の最小化に焦点が当てられてい る。しかしながら、このセル寸法最小化の圧力は、セル容量最大化の要求と矛盾してしまう。このセル容量 最大化要求は、メモリ・セル設計者にプレッシャーをかけ、セル寸法を縮小しながら容量の最低必要条件を 満たすように設計と材料にわたって創造的な手段を探求させている。その上、最小面積に最大数の DRAM セルを密に実装するためには、セル・ピッチの最小化が必要となる。

マイクロプロセッサでも、最高性能を保ちつつコスト削減を達成するという市場圧力が強くかかっている。主にトランジスタ・ゲート長と配線層数により、高性能が可能なものとなる。ORTC表に関する所要の機能、チップ寸法、セル面積、密度などについて、2003年版ITRSチームは意見の一致をみている。モデルの考えを伝えるために追加項目が加えられ、基本モデル仮定条件が注記されている。短期と長期の技術ノード数値の要約を表 1a と表 1b に示す。同意されたように、主要 ITRS 技術ノードを代表する数値は引き続きDRAM ハーフピッチだろうと思われるが、積極的に MPU ゲート長を縮少し性能を促進する素子寸法もまた含まれている。表の完全性を図るため、MPU/ASIC製品-メタル・ハーフピッチも検討して載せており、そのペースは、わずかに DRAM ハーフピッチに遅れるかまたは等しくなっている。ASIC/低電力のゲート長も含まれてはいるが、待機電流および動作電流を最大にするために最先端 MPU よりは遅れている。ハーフピッチとゲート長の機能に関する詳細な定義については、用語集セクションを参照して頂きたい。各製品世代について、最先端の(「現在導入中」)DRAM製品と量産(「現在量産中」)DRAM製品の双方を示す。

1995 年 ~ 2001 年の間に、像寸法における長期の年間平均縮小率が約 16%/年(約 30%縮小/2 年)に加速してはいるが、この縮小率を約 11%/年(約 30%縮小/3 年)であると継続して予測していることに注意して頂きたい(図 5 参照)。上述のとおり、新規製品世代導入の全体スケジュールは、1 年間短縮のペースで加速されてきている。

| Year of Production                                      | 2003 | 2004 | 2005 | 2006 | 2007 | 2008 | 2009 |

|---------------------------------------------------------|------|------|------|------|------|------|------|

| Technology Node                                         |      | hp90 |      |      | hp65 |      |      |

| DRAM ½ Pitch (nm)                                       | 100  | 90   | 80   | 70   | 65   | 57   | 50   |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                      | 120  | 107  | 95   | 85   | 76   | 67   | 60   |

| MPU/ASIC ½ Pitch (nm) (Un-contacted Poly)               | 107  | 90   | 80   | 70   | 65   | 57   | 50   |

| MPU Printed Gate Length (nm) ††                         | 65   | 53   | 45   | 40   | 35   | 32   | 28   |

| MPU Physical Gate Length (nm)                           | 45   | 37   | 32   | 28   | 25   | 22   | 20   |

| ASIC/Low Operating Power Printed Gate<br>Length (nm) †† | 90   | 75   | 65   | 53   | 45   | 40   | 35   |

| ASIC/Low Operating Power Physical Gate<br>Length (nm)   | 65   | 53   | 45   | 37   | 32   | 28   | 25   |

表 1a 製品世代およびチップ寸法モデルのテクノロジ・ノード―短期

表 1b 製品世代およびチップ寸法モデルのテクノロジ・ノード—長期

| Year of Production                                      | 2010 | 2012 | 2013 | 2015 | 2016 | 2018 |

|---------------------------------------------------------|------|------|------|------|------|------|

| Technology Node                                         | hp45 |      | hp32 |      | hp22 |      |

| DRAM ½ Pitch (nm)                                       | 45   | 35   | 32   | 25   | 22   | 18   |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                      | 54   | 42   | 38   | 30   | 27   | 21   |

| MPU/ASIC ½ Pitch (nm) (Un-contacted Poly)               | 45   | 35   | 32   | 25   | 22   | 18   |

| MPU Printed Gate Length (nm) ††                         | 25   | 20   | 18   | 14   | 13   | 10   |

| MPU Physical Gate Length (nm)                           | 18   | 14   | 13   | 10   | 9    | 7    |

| ASIC/Low Operating Power Printed Gate<br>Length (nm) †† | 32   | 25   | 22   | 18   | 16   | 13   |

| ASIC/Low Operating Power Physical Gate<br>Length (nm)   | 22   | 18   | 16   | 13   | 11   | 9    |

# 表 la と lb の注記:

††MPU および ASIC のゲート長(レジストにおける) ノードの目標とは、フォトレジストにアズプリンテッド(as printed in photoresist) という最も積極的な要件を指している(1999 年版 ITRS では「ポリシリコンにアズエッチド(as etched in polysilicon)」と定義)。

しかしながら、2000/2001 年版 ITRS の開発時に、「アズプリンテッド」寸法から「物理」ゲート長を縮小できる傾向が特定された。ロジック・マイクロプロセッサ(MPU)製品の速度性能最大化という要求により、これらの「物理」ゲート長の目標は推し進められている。また、デバイス設計とプロセス技術の要求を推進するニーズとして、これらの目標は、フロントエンド・プロセス (Front End Processes: FEP)、プロセス・インテグレーション、デバイス、構造 (Process Integration, Devices, and Structures: PIDs)、設計 (Design) の各 ITWG 表に含まれている。

加えるに、2003 年版ITRSの開発の間、2003 年に 90nm 技術ノードの製造を多くのロジック製造メーカが新聞発表したことに対する調整が行なわれた。実際のデバイスのメタル1 (M1)のハーフピッチが 110-120nm と述べられていたので、ITRSのDRAMハーフピィチに基づくヘッダー目標との間で混乱が生じた。先端デバイスの製造メーカと話し合った後、一般への発表は密度を表すためのハーフピッチと速度性能を表すためのプリント・ゲート長の平均の数値をヘッダーに用いて各社は技術ノード・ロードマップを示していることが分った。

IRCはITRSと個別の会社が行なう一般への発表との混乱を最小化にするために、ITRSの表のヘッダー・ノードを業界で最も挑戦的なハーフピッチとし、この目標をhpXX(即ち、hp90、hp65、hp45、等)と表記する事とした。現在の所、業界の最も挑戦的ハーフピッチはDRAMセルのメタル・ハーフピッチである。

製品の導入、量産、世代間、世代内の用語については、用語集を参照のこと。

表 1c DRAM 生産の製品世代およびチップ寸法モデル―短期

| Year of Production                               | 2003   | 2004   | 2005   | 2006   | 2007   | 2008   | 2009      |

|--------------------------------------------------|--------|--------|--------|--------|--------|--------|-----------|

| Technology Node                                  |        | hp90   |        |        | hp65   |        |           |

| DRAM ½ Pitch (nm)                                | 100    | 90     | 80     | 70     | 65     | 57     | <i>50</i> |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)               | 120    | 107    | 95     | 85     | 76     | 67     | 60        |

| MPU/ASIC ½ Pitch (nm) (Un-contacted Poly)        | 107    | 90     | 80     | 70     | 65     | 57     | 50        |

| MPU Printed Gate Length (nm) ††                  | 65     | 53     | 45     | 40     | 35     | 32     | 28        |

| MPU Physical Gate Length (nm)                    | 45     | 37     | 32     | 28     | 25     | 22     | 20        |

| Cell area factor [a]                             | 8      | 8      | 7.5    | 7      | 7      | 6      | 6         |

| Cell area [Ca = af²] (mm²)                       | 0.082  | 0.065  | 0.048  | 0.036  | 0.028  | 0.019  | 0.015     |

| Cell array area at production (% of chip size) § | 63.00% | 63.00% | 63.00% | 63.00% | 63.00% | 63.00% | 63.00%    |

| Generation at production §                       | 1G     | 1G     | 1G     | 2G     | 2G     | 4G     | 4G        |

| Functions per chip (Gbits)                       | 1.07   | 1.07   | 1.07   | 2.15   | 2.15   | 4.29   | 4.29      |

| Chip size at production (mm²)§                   | 139    | 110    | 82     | 122    | 97     | 131    | 104       |

| Gbits/cm² at production §                        | 0.77   | 0.97   | 1.31   | 1.76   | 2.22   | 3.27   | 4.12      |

表 1d DRAM 生産の製品世代およびチップ寸法モデル―長期

| Year of Production                               | 2010   | 2012   | 2013   | 2015   | 2016   | 2018   |

|--------------------------------------------------|--------|--------|--------|--------|--------|--------|

| Technology Node                                  | hp45   |        | hp32   |        | hp22   |        |

| DRAM ½ Pitch (nm)                                | 45     | 35     | 32     | 25     | 22     | 18     |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)               | 54     | 42     | 38     | 30     | 27     | 21     |

| MPU/ASIC ½ Pitch (nm) (Un-contacted Poly)        | 45     | 35     | 32     | 25     | 22     | 18     |

| MPU Printed Gate Length (nm) ††                  | 25     | 20     | 18     | 14     | 13     | 10     |

| MPU Physical Gate Length (nm)                    | 18     | 14     | 13     | 10     | 9      | 7      |

| Cell area factor [a]                             | 6      | 6      | 6      | 6      | 5      | 5      |

| Cell area [Ca = af²] (mm²)                       | 0.012  | 0.0077 | 0.0061 | 0.0038 | 0.0025 | 0.0016 |

| Cell array area at production (% of chip size) § | 63.00% | 63.0%  | 63.0%  | 63.0%  | 63.0%  | 63.0%  |

| Generation at production §                       | 4G     | 8G     | 8G     | 16g    | 32G    | 32G    |

| Functions per chip (Gbits)                       | 4.29   | 8.59   | 8.59   | 17.18  | 34.36  | 34.36  |

| Chip size at production (mm²)§                   | 83     | 104    | 83     | 104    | 138    | 87     |

| Gbits/cm² at production §                        | 5.19   | 8.23   | 10.37  | 16.46  | 24.89  | 39.51  |

#### 表 1c と 1d の注記:

§DRAM モデル - セル・ファクタ(設計/プロセスの改善目標)を以下に示す。

1999-2004/8×;2005/7 . 5×; 2006-2007/7×; 2008-2015/6×; 2016-2018/5×. 「6」のDRAMセル設計改善

ファクター[a]の 2003 年から 2008 年への 5 年の遅れのために、「ムーアの法則」はチップ当たりビット数で 1.5 から 2 年で 2 倍にから、2003 年版ITRS・DRAMチップ寸法モデルの 2.5 年から 3 年で 2 倍にへになり、2004 年以降は 3 年のDRAMハーフピッチ・ノード・サイクルに落ち着く。

下記を除いて、DRAM 生産世代は、間に 2×ビット/チップの暫定的な世代があるが、4 年ごとに 4×ビット/チップの割合で一般的に増加している。

- 1. 導入(Introduction)フェーズにおいて、16G ビット中間世代の後、導入レートは 4×/5 年(2×/3 年) である。

- 2. 量産(Production)フェーズにおいて、1G ビット世代の後、導入レートは 4×/5 年(2×/2 ~ 3 年) である。

量産フェーズのDRAMの世代間(InTER-generation)チップ寸法成長率モデル目標は、今やMPUのモデルと同様に  $140 \text{mm}^2$ 以下で一定である。この新しい一定チップ寸法モデル目標でチップ当たりビット数の「ムーア」の法則DRAMモデルはチップ当たりのビット数が 2 倍になるのに、 $2 \times / 2$  年と  $2 \times / 3$  年を繰り返して平均  $2 \times / 2$  . 5 年に延長した(ORTC表 1 c、dを参照)。加えるに、セル・アレー効率(全チップ面性に対するメモリー・アレーの%)は 63%に増加し、このため、量産フェーズの製品チップ寸法が、セル設計改善ファクターの遅れ(上の記述参照)にもかかわらず、チップ寸法一定のモデル目標を達成すことが出来るようになった。世代内(InTRA-generation)チップ寸法シュリンクモデルは、セル・ファクタ縮小の中間でのテクノロジ・ノードごとに  $0.5 \times$ である。

用語 - 導入(Introduction)、生産(Production)、世代間(InTER-generation)、世代内(InTRA-generation)については、用語集を参照して頂きたい。

表 1e DRAM 導入の製品世代およびチップ寸法モデル―短期

| Year of Production                                 | 2003   | 2004   | 2005   | 2006   | 2007   | 2008   | 2009   |

|----------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|

| Technology Node                                    |        | hp90   |        |        | hp65   |        |        |

| DRAM ½ Pitch (nm)                                  | 100    | 90     | 80     | 70     | 65     | 57     | 50     |

| DRAM ½ Pitch (nm)                                  | 100    | 90     | 80     | 70     | 65     | 57     | 50     |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                 | 120    | 107    | 95     | 85     | 76     | 67     | 60     |

| MPU/ASIC ½ Pitch (nm) (Un-contacted Poly)          | 107    | 90     | 80     | 70     | 65     | 57     | 50     |

| MPU Printed Gate Length (nm) ††                    | 65     | 53     | 45     | 40     | 35     | 32     | 28     |

| MPU Physical Gate Length (nm)                      | 45     | 37     | 32     | 28     | 25     | 22     | 20     |

| Cell area factor [a]                               | 8      | 8      | 7.5    | 7      | 7      | 6      | 6      |

| Cell area [Ca = af²] (mm²)                         | 0.082  | 0.065  | 0.048  | 0.036  | 0.028  | 0.019  | 0.015  |

| Cell array area at introduction (% of chip size) § | 72.23% | 72.61% | 72.95% | 73.25% | 73.52% | 73.76% | 73.97% |

| Generation at introduction §                       | 4G     | 4G     | 8G     | 8G     | 16G    | 16G    | 16G    |

| Functions per chip (Gbits)                         | 4.29   | 4.29   | 8.59   | 8.59   | 17.18  | 17.18  | 17.18  |

| Chip size at introduction (mm²) §                  | 485    | 383    | 568    | 419    | 662    | 449    | 356    |

| Gbits/cm² at introduction §                        | 0.88   | 1.12   | 1.51   | 2.05   | 2.59   | 3.82   | 4.83   |

| Year of Production                                 | 2010   | 2012   | 2013   | 2015   | 2016   | 2018   |

|----------------------------------------------------|--------|--------|--------|--------|--------|--------|

| Technology Node                                    | hp45   |        | hp32   |        | hp22   |        |

| DRAM ½ Pitch (nm)                                  | 45     | 35     | 32     | 25     | 22     | 18     |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                 | 54     | 42     | 38     | 30     | 27     | 21     |

| MPU/ASIC ½ Pitch (nm) (Un-contacted Poly)          | 45     | 35     | 32     | 25     | 22     | 18     |

| MPU Printed Gate Length (nm) ††                    | 25     | 20     | 18     | 14     | 13     | 10     |

| MPU Physical Gate Length (nm)                      | 18     | 14     | 13     | 10     | 9.0    | 7.0    |

| Cell area factor [a]                               | 6      | 6      | 6      | 6      | 5      | 5      |

| Cell area [Ca = af2] (mm²)                         | 0.012  | 0.0077 | 0.0061 | 0.0038 | 0.0025 | 0.0016 |

| Cell array area at introduction (% of chip size) § | 74.16% | 74.47% | 74.61% | 74.83% | 74.93% | 75.09% |

| Generation at introduction §                       | 32G    | 32G    | 64G    | 64G    | 128G   | 128G   |

| Functions per chip (Gbits)                         | 34.36  | 34.36  | 68.72  | 68.7   | 137.4  | 137.4  |

| Chip size at introduction (mm²) §                  | 563    | 353    | 560    | 351    | 464    | 292    |

| Gbits/cm2 at introduction §                        | 5.2    | 8.2    | 10.4   | 16.5   | 24.9   | 39.5   |

表 1f DRAM 導入の製品世代およびチップ寸法モデル―長期

### 表 le と lf の注記:

§DRAM モデル・セル・ファクタ(設計/プロセスの改善目標)を以下に示す。

1999-2004/8×;2005/7 . 5×; 2006-2007/7×; 2008-2015/6×; 2016-2018/5×. 「6」のDRAMセル設計改善

ファクター[a]の 2003 年から 2008 年への 5 年の遅れのために、「ムーアの法則」はチップ当たりビット数で 1.5 から 2 年で 2 倍 にから、2003 年版ITRS・DRAMチップ寸法モデルの 2.5 年から 3 年で 2 倍になり、2004 年以降は 3 年のDRAMハーフピ ッチ・ノード・サイクルに落ち着く。.

下記を除いて、DRAM 生産世代は、間に 2×ビット/チップの暫定的な世代があるが、4 年ごとに 4×ビット/チップの割合で一般 的に増加している。

- 1. 導入フェーズにおいて、16G ビット中間世代/2007 年の後、導入レートは 4×/5 年(2×/3 年) である。

- 2. 生産フェーズにおいて、1G ビット世代/2003 年の後、導入レートは 4×/5 年(2×/2 ~ 3 年) である。

元々の 2001 年版ITRSでは、チップ寸法の世代間成長率は、導入時に 572mm2フィールド(field)あたり 1 チップ、および量 産時に 572mm<sup>2</sup>フィールドあたり 2 チップを保つようにしている。セル・エリア・ファクター低減の遅れから、導入チップのチップ 寸法は増加したが、新しい最大 704mm<sup>2</sup> 可能な露光領域で導入チップの 2 年毎にビット数を 2 倍にすることは、16G bit世代 (660mm²/2007)まで可能である。「ムーアの法則」の導入フェーズDRAMのチップ当たりのビット数が平均して 2×/2.5 年に 遅れたことで、2007年以降、導入フェーズDRAMは元々の 572mm²より小さな実現性のある寸法目標となった。 世代内チッ プ寸法シュリンクモデルは、セル・ファクタ縮小の中間でのテクノロジ・ノードごとに 0.5×であり、最終的には(5 から 6 年の内 に)、導入フェーズのDRAMは  $140 \text{mm}^2$ 以下の量産フェーズのチップ寸法目標にシュリンクする。

用語 - 導入、量産、世代間、世代内については、用語集を参照して頂きたい。

表 1g MPU (大容量マイクロプロセッサ) コスト重視製品世代およびチップ寸法モデル―短期

| Year of Production                  | 2003 | 2004 | 2005 | 2006 | 2007 | 2008 | 2009 |

|-------------------------------------|------|------|------|------|------|------|------|

| Technology Node                     |      | hp90 |      |      | hp65 |      |      |

| DRAM ½ Pitch (nm)                   | 100  | 90   | 80   | 70   | 65   | 57   | 50   |

| DRAM ½ Pitch (nm)                   | 100  | 90   | 80   | 70   | 65   | 57   | 50   |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)  | 120  | 107  | 95   | 85   | 76   | 67   | 60   |

| MPU/ASIC ½ Pitch (nm) (Un-contacted |      |      |      |      |      |      |      |

| Poly)                               | 107  | 90   | 80   | 70   | 65   | 57   | 50   |

| MPU Printed Gate Length (nm) ††     | 65   | 53   | 45   | 40   | 35   | 32   | 28   |

| MPU Physical Gate Length (nm)                                                            | 45    | 37    | 32    | 28    | 25    | 22    | 20    |

|------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|

| SRAM Cell (6-transistor) Area factor                                                     | 120.3 | 117.8 | 115.6 | 113.7 | 111.9 | 110.4 | 109.0 |

| Logic Gate (4-transistor) Area factor ++                                                 | 320   | 320   | 320   | 320   | 320   | 320   | 320   |

| SRAM Cell (6-transistor) Area<br>efficiency ++                                           | 0.63  | 0.63  | 0.63  | 0.63  | 0.63  | 0.63  | 0.63  |

| Logic Gate (4-transistor) Area<br>efficiency ++                                          | 0.50  | 0.50  | 0.50  | 0.50  | 0.50  | 0.50  | 0.50  |

| SRAM Cell (6-transistor) Area<br>w/overhead ++                                           | 2.0   | 1.5   | 1.2   | 0.93  | 0.73  | 0.57  | 0.45  |

| Logic Gate (4-transistor) Area<br>w/overhead ++                                          | 6.5   | 5.2   | 4.1   | 3.3   | 2.6   | 2.1   | 1.6   |

| Transistor density SRAM<br>(Mtransistors/cm²)                                            | 305   | 393   | 504   | 646   | 827   | 1,057 | 1,348 |

| Transistor density logic<br>(Mtransistors/cm²)                                           | 61    | 77    | 97    | 122   | 154   | 194   | 245   |

| Generation at introduction *                                                             |       | р07с  |       |       | р10с  |       |       |

| Functions per chip at introduction (million transistors [Mtransistors])                  | 180   | 226   | 285   | 360   | 453   | 571   | 719   |

| Chip size at introduction (mm²) ‡                                                        | 280   | 280   | 280   | 280   | 280   | 280   | 280   |

| Cost performance MPU<br>(Mtransistors/cm² at introduction)<br>(including on-chip SRAM) ‡ | 110   | 138   | 174   | 219   | 276   | 348   | 438   |

| Generation at production *                                                               |       | р04с  |       |       | р07с  |       |       |

| Functions per chip at production<br>(million transistors [Mtransistors])                 | 153   | 193   | 243   | 307   | 386   | 487   | 614   |

| Chip size at production (mm²) §§                                                         | 140   | 140   | 140   | 140   | 140   | 140   | 140   |

| Cost performance MPU<br>(Mtransistors/cm² at production,<br>including on-chip SRAM) ‡    | 110   | 138   | 174   | 219   | 276   | 348   | 438   |

# 表 1h MPU (大容量マイクロプロセッサ) コスト重視製品世代およびチップ寸法モデル―長期

| Year of Production                             | 2010  | 2012  | 2013  | 2015  | 2016  | 2018  |

|------------------------------------------------|-------|-------|-------|-------|-------|-------|

| Technology Node                                | hp45  |       | hp32  |       | hp22  |       |

| DRAM ½ Pitch (nm)                              | 45    | 35    | 32    | 25    | 22    | 18    |

| DRAM ½ Pitch (nm)                              | 45    | 35    | 32    | 25    | 22    | 18    |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)             | 54    | 42    | 38    | 30    | 27    | 21    |

| MPU/ASIC ½ Pitch (nm) (Un-contacted Poly)      | 45    | 35    | 32    | 25    | 22    | 18    |

| MPU Printed Gate Length (nm) ††                | 25    | 20    | 18    | 14    | 13    | 10    |

| MPU Physical Gate Length (nm)                  | 18    | 14    | 13    | 10    | 9     | 7     |

| SRAM Cell (6-transistor) Area factor ++        | 107.8 | 105.7 | 104.8 | 103.4 | 102.8 | 101.7 |

| Logic Gate (4-transistor) Area factor ++       | 320   | 320   | 320   | 320   | 320   | 320   |

| SRAM Cell (6-transistor) Area<br>efficiency ++ | 0.625 | 0.625 | 0.625 | 0.625 | 0.625 | 0.625 |

| Logic Gate (4-transistor) Area efficiency      | 0.500 | 0.500 | 0.500 | 0.500 | 0.500 | 0.500 |

| SRAM Cell (6-transistor) Area<br>w/overhead ++ | 0.22  | 0.13  | 0.11  | 0.066 | 0.052 | 0.032 |

| Logic Gate (4-transistor) Area<br>w/overhead ++                                          | 1.30  | 0.82  | 0.65  | 0.41  | 0.32  | 0.20   |

|------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|--------|

| Transistor density SRAM<br>(Mtransistors/cm²)                                            | 1,718 | 2,781 | 3,532 | 5,687 | 7,208 | 11,558 |

| Transistor density logic<br>(Mtransistors/cm²)                                           | 309   | 490   | 617   | 980   | 1,235 | 1,960  |

| Generation at introduction *                                                             | р13с  |       | p16c  |       | р19с  |        |

| Functions per chip at introduction (million transistors [Mtransistors])                  | 1,546 | 2,454 | 3,092 | 4,908 | 6,184 | 9,816  |

| Chip size at introduction (mm²) ‡                                                        | 280   | 280   | 280   | 280   | 280   | 280    |

| Cost performance MPU<br>(Mtransistors/cm² at introduction)<br>(including on-chip SRAM) ‡ | 552   | 876   | 1,104 | 1,753 | 2,209 | 3,506  |

| Generation at production *                                                               | р10с  |       | p13c  |       | p16c  |        |

| Functions per chip at production (million transistors [Mtransistors])                    | 773   | 1,227 | 1,546 | 2,454 | 3,092 | 4,908  |

| Chip size at production (mm²) §§                                                         | 140   | 140   | 140   | 140   | 140   | 140    |

| Cost performance MPU<br>(Mtransistors/cm² at production,<br>including on-chip SRAM) ‡    | 552   | 876   | 1,104 | 1,753 | 2,209 | 3,506  |

### 表 1g と 1h の注記:

- ++ MPU エリヤ・ファクタは DRAM の「セル・エリヤ・ファクタ」に類似している。 今まで、 エリヤ・ファクタの縮小は、 数多 くの要因の組合せにより達成されてきている。その要因とは、たとえば、配線層の追加、自己整合手法、効率的な回路 レイアウトなどがある。しかしながら、最近のデータによれば、エリヤ・ファクタの改善(縮小)ペースは低下しており、ロジ ック・ゲートのエリヤ・ファクタについては、事実上一定で(フラットで)あることが示されている。

- \* pはプロセッサであり、数値は生産の年を表す。cはコスト重視製品を示す。例 コスト重視プロセッサ p01cは 1999 年に導入されたが、2001 年になって量産された。同様に、p04c は 2001 年に導入されるが、2004 年に量産が予定され ている。

- \* MPU コスト重視モデル: コスト重視 MPU はレベル 2(L2)オンチップ SRAM(512Kbyte/1999)が含まれている。 SRAMとロジック・トランジスタ両方の機能の組合せはテクノロジ・ノード・サイクルごとに倍増する。

§§MPU チップ寸法モデル: コスト重視 MPU と高性能 MPU の世代間チップ寸法成長率は、2018年(280mm2/コスト 重視MPU導入時; 140mm2/コスト重視MPU量産時; 310mm2/高性能MPU量産時)まで一定とされている。MP Uのチップ寸法一定のモデルはテクノロジ・ノード・サイクルごとのオンチップ機能の倍増により可能となる。世代内チッ プ寸法シュリンクモデルは、2001 年まで 2 年テクノロジ・ノードごとに 0.5×であり、2003 年以降の今や 3 年テクノロジ・ノ ードごとに 0.5×である。

定義は用語集参照のこと。

表 1i 高性能 MPU および ASIC 製品世代およびチップ寸法モデル―短期

| Year of Production                        | 2003 | 2004 | 2005 | 2006 | 2007 | 2008 | 2009 |

|-------------------------------------------|------|------|------|------|------|------|------|

| Technology Node                           |      | hp90 |      |      | hp65 |      |      |

| DRAM ½ Pitch (nm)                         | 100  | 90   | 80   | 70   | 65   | 57   | 50   |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)        | 120  | 107  | 95   | 85   | 76   | 67   | 60   |

| MPU/ASIC ½ Pitch (nm) (Un-contacted Poly) | 107  | 90   | 80   | 70   | 65   | 57   | 50   |

| MPU Printed Gate Length (nm) ††           | 65   | 53   | 45   | 40   | 35   | 32   | 28   |

| MPU Physical Gate Length (nm)             | 45   | 37   | 32   | 28   | 25   | 22   | 20   |

| Logic (Low-volume Microprocessor) High-perform                                                             | nance ‡ |       |       |       |       |       |       |

|------------------------------------------------------------------------------------------------------------|---------|-------|-------|-------|-------|-------|-------|

| Generation at production **                                                                                | p03h    |       | p05h  |       | p07h  |       | p09h  |

| Functions per chip (million transistors)                                                                   | 439     | 553   | 697   | 878   | 1,106 | 1,393 | 1,756 |

| Chip size at production (mm²) §§                                                                           | 310     | 310   | 310   | 310   | 310   | 310   | 310   |

| High-performance MPU Mtransistors/cm² at production (including on-chip SRAM) ‡                             | 142     | 178   | 225   | 283   | 357   | 449   | 566   |

| ASIC                                                                                                       |         |       |       |       |       |       |       |

| ASIC usable Mtransistors/cm² (auto layout)                                                                 | 142     | 178   | 225   | 283   | 357   | 449   | 566   |

| ASIC max chip size at production (mm²)<br>(maximum lithographic field size)                                | 572     | 572   | 572   | 572   | 572   | 572   | 572   |

| ASIC maximum functions per chip at production (Mtransistors/chip) (fit in maximum lithographic field size) | 810     | 1,020 | 1,286 | 1,620 | 2,041 | 2,571 | 3,239 |

表 1 高性能 MPU および ASIC 製品世代およびチップ寸法モデル―長期

| Year of Production                                                                                         | 2010  | 2012  | 2013  | 2015   | 2016   | 2018   |

|------------------------------------------------------------------------------------------------------------|-------|-------|-------|--------|--------|--------|

| Technology Node                                                                                            | hp45  |       | hp32  |        | hp22   |        |

| DRAM ½ Pitch (nm)                                                                                          | 45    | 35    | 32    | 25     | 22     | 18     |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                                                         | 54    | 42    | 38    | 30     | 27     | 21     |

| MPU/ASIC ½ Pitch (nm) (Un-contacted Poly)                                                                  | 45    | 35    | 32    | 25     | 22     | 18     |

| MPU Printed Gate Length (nm) ††                                                                            | 25    | 20    | 18    | 14     | 13     | 10     |

| MPU Physical Gate Length (nm)                                                                              | 18    | 14    | 13    | 10     | 9      | 7      |

| Logic (Low-volume Microprocessor) High-performan                                                           | ice‡  |       |       |        |        |        |

| Generation at production **                                                                                |       |       | p13h  | p15h   |        |        |

| Functions per chip (million transistors)                                                                   | 2,212 | 3,511 | 4,424 | 7,022  | 8,848  | 14,045 |

| Chip size at production (mm²) §§                                                                           | 310   | 310   | 310   | 310    | 310    | 310    |

| High-performance MPU Mtransistors/cm² at production (including on-chip SRAM) ‡                             | 714   | 1,133 | 1,427 | 2,265  | 2,854  | 4,531  |

| ASIC                                                                                                       | •     |       |       |        |        |        |

| ASIC usable Mtransistors/cm² (auto layout)                                                                 | 714   | 1,133 | 1,427 | 2,265  | 2,854  | 4,531  |

| ASIC maximum chip size at production (mm²)<br>(maximum lithographic field size)                            | 572   | 572   | 572   | 572    | 572    | 572    |

| ASIC maximum functions per chip at ramp<br>(Mtransistors/chip)<br>(fit in maximum lithographic field size) | 4,081 | 6,479 | 8,163 | 12,958 | 16,326 | 25,915 |

#### 表 li と lj の注記:

- \*\* p はプロセッサであり、数値は量産の年を表す。h は高性能製品を示す。例 高性能プロセッサ p99hは 1999 年に量産へと立上げられた。同様に、p01c は 2001 年に導入され、p03h は 2003 年にと。

- ‡ MPU 高性能モデル: 高性能 MPU は大型 L2 と L3 オンチップ SRAM(2M バイト/1999 年)+大型ロジック・コア (P99h コア = 25M トランジスタ)を含む。 SRAM とロジック両方はテクノロジ・ノード・サイクルごとに倍増する。

- §§ MPU チップ寸法モデル: コスト重視 MPU と高性能 MPU の世代間チップ寸法成長率は、2018 年まで一定とされている(280mm2/コスト重視 MPU 導入時; 140mm2/コスト重視 MPU 量産時; 310mm2 / 高性能 MPU 量産時)。この MPUのチップ寸法一定モデルは、テクノロジ・ノード・サイクルごとのオンチップ機能の倍増により可能となる。世代内チップ寸法シュリンクモデルは、2001 年まで 2 年テクノロジ・ノードごとに 0.5×であり、2003 年以降は 3 年テクノロジ・

ノードごとに 0.5×である。 定義は用語集を参照

# チップ・サイズ、リソグラフィ・フィールド、ウェーハ・サイズの各傾向

3年ごとに継続して素子寸法が約 30%縮小するにもかかわらず、IEEE (Institute of Electrical and Electronics Engineers:米国電気電子学会)国際固体素子会議などの技術フォーラムにおいて DRAM 製品を最初にデモンストレーションする時のサイズは、6年ごとに倍増している(年間約 12%増)。(今までは、1.5~2 年ごとに機能が倍増する)ムーアの法則に従い、ビット/キャパシタ/トランジスタを年間 59%増の割合で収容するために、このチップ・エリヤの増加が必要となる。しかしながら、コスト/機能が年間~25—30%縮小するという今までの傾向を維持するには、設備生産性の増強、製造歩留りの向上、最大サイズ・ウェーハの使用、とりわけ、1枚のウェーハ上の使用可能なチップ数の増加が継続的に必要となる。

1 枚のウェーハ上の使用可能なチップ総数の増加は、主として素子サイズの小型化(縮小/スケーリング) と製品/プロセスの再設計(圧縮)の組合せにより達成される。たとえば、最新モデルを使って、低コスト製品世代[世代間(世代対世代)機能を 2 年ごとに倍増]の初期のチップ・サイズは一定のままにとどまるか、可能な限り維持することが予測されている。さらに、各テクノロジ・ノード期間では、世代内(世代の中)年間縮小比率 50%(0.7×のリソグラフィ縮小比率の二乗)で、チップ・サイズを縮小することが必要となっている。

手ごろな値段で購入できる DRAM 製品でも、世代内で仮想的にチップ・サイズを一定に維持するために、トータル・チップ・エリヤの 63%というセル・エリヤ・アレイ効率も維持しなければならない。従って、DRAM 製品はセル・エリヤ・デザイン・ファクタ(最小機能サイズの二乗で表したセル・エリヤ)を小さくすることが必要となる。PIDS と FEP ITWG はアレイ効率目標、セルエリアファクター、およびチップあたりのビット数のメンバー調査データを提供している。さらにフロントエンド・プロセスの章に、セル・エリヤ目標を達成する解決策へのチャレンジとニーズが詳述されている。これら新しいチャレンジを追尾(tracking)/調整することが非常に重要なので、DRAM セル・エリヤ・ファクタ、目標エリヤ・サイズ、トータル・チップ・サイズに対するセル・アレイ・エリヤの割合などの項目は ORTC 表 1c、1d、1e、1fにて追尾を継続していくこととなる(詳細については、用語集参照)。特に 2003 年の ITRS モデルでの DRAM セルエリアファクターのリダクションレートは著しく遅くなっている(セルエリアファクター6 は 2003 年から 2008 年に、セルエリアファクター4 は 5 に代わりさらに 2011 年から 2016 年にシフトした)。チップ・サイズ維持するという目標を維持するため、2003 年ITRS の DRAM チップ・サイズ・モデルでは今まで以上に積極的なアレー効率目標を持ち、さらに More's Law が示すチップあたりのビット数の増加割合は 3 年で 2 倍から 3 年で 2 倍に減速されている。

2001年の ITRS には、設計 ITWG により MPU チップ・サイズ・モデルが改良されて、最新のトランジスタ密度、大型オンチップ SRAM、小型目標チップ・サイズで MPU チップ・サイズ・モデルがアップデートされた。 設計 ITWG は、トランジスタ設計改善ファクタを含む追加詳細項目がモデルに追加されてもいる。 設計 ITWG は、SRAMトランジスタの設計改善は、スローペースで行われており、ロジック・ゲート・トランジスタでは設計改善が殆ど行われていないと述べている。 ほとんど全ての「縮小」と密度改善はリソグラフィにより可能となった配線ハーフピッチのスケーリングによりもたらされている。

今回の 2003 年 ITRS の MPU チップ・サイズ・モデルは 2001 年ITRS と同じで、引き続き高性能 MPU(310mm2)およびコスト-性能 MPU(140mm2)双方におけるチップ・サイズ維持の傾向を考慮し、手ごろな値段と電力管理についての競争的な要求を反映している。2004 年までの MPU 2 年サイクル・ハーフピッチ「追いつきフェーズ」により、リソグラフィの改善だけで MPU 製品は一定のチップ・サイズを保つことができる。しかし 2004 年以降、ITRS の技術世代に示されている世代間 MPU チップ・サイズのモデルでは、各テ

クノロジ・ノードごとにオンチップ・トランジスタの数を倍増させるペースを減速させることによってのみ、一定にとどめることができる。

3 年テクノロジ・ノード・サイクルに予測された結果により、現在の MPU チップ・サイズ・モデルは、オンチップ・トランジスタに関するムーアの法則の割合を 3 年ごとに倍増へと低下させる。チップ・サイズ一定の目標を達成しかつ 2 年ごとにオンチップ機能(トランジスタ)倍増という今までの傾向を達成するためには、MPU のチップ設計者およびプロセス設計者は、基本的なリソグラフィ・ベース型スケーリング傾向に設計/プロセスの改善を追加しなければならない。表 1g、1h、1i、1jに MPU モデルの新しい目標値を要約して示す。

生産性を向上するには、製作プロセスの各ステップで良好なチップの生産量を増加しなければならない。 1 回の露光で複数チップをプリントする能力は主な生産性の原動力であり、その原動力はリソグラフィ・ツールのフィールド・サイズ、およびウェーハにプリントされるチップのサイズとアスペクト比により決定されている。 今までのリソグラフィ露光フィールドは、2 世代のテクノロジ・ノードごとに倍増してチップ・サイズ増大の需要を満たしていた。その結果、1999年には非常に広いステップ走査フィールド(25 X 32 = 800mm²)が達成された。しかし、リソグラフィITWGにより、継続的に解像力の向上を図りながら大きなフィールド・サイズを保つことは、大幅なコスト上昇を招ことが示された。そのため、ITWGにより、90 nm ノードまでに経済的に手ごろな値段のリソグラフィ・フィールドを 572mm2 レベル (22 X 26)に縮小する要件が検討されていた。しかしITWGでの更なる議論により、2003年のITRSでは可能なフィールド・サイズを704mm2(22 X 32)に増加させた。この傾向を表 2a、2bに示す。

DRAM チップ・サイズは、受け入れ可能なリソグラフィ・フィールド・サイズを最も適切に示すと見なされていた。2003 年の ITRS の DRAM チップ・サイズ・モデルでは、導入レベルのチップ・サイズを新しい受け入れ可能な 704mm²リソグラフィ・フィールドよりも小さくして、少なくとも 1 個の導入レベル・チップ・サイズがフィールド内に収まるようにしている。新しい生産レベル DRAM モデル(140mm²より小さいチップ・サイズ維持を目標)では、少なくとも 4 個の導入レベル・チップ・サイズを手ごろなフィールド内に収めている。テクノロジ・ノード・スケーリングとセル設計改善(A ファクタの縮小)との組合せにより、2 年ごとにオンチップ・ビットの倍増を果たしながら、この目標を達成することが可能となる。しかし上述したように、DRAM 設計改善スピードの低下により、受け入れ可能なリソグラフィ・フィールドの限界内にとどめるために、追加するオンチップ・ビット数を減らすという要求がもたらされている。これは、現在の DRAM モデルでムーアの法則が示すビット/チップ・レートを 2 倍/2.5 から 3 年へと下げることにより達成することができる。DRAM モデルのデ□ タ目標を表 1c、1d、1e、1fに載せる。

DRAM モデルと MPU モデルは双方とも、DRAM と MPU の設計およびプロセスの改善目標を達成できるかどうかにかかっている。達成できない場合は、現在のロードマップが示したのより大きなチップ・サイズをプリントする方向への圧力が高まるか、または、オンチップ機能に関するムーアの法則のレートがさらに低下する。いずれの結果でも、コスト/機能の縮小レート(半導体産業の生産性向上と競争力に関するクラシカルな尺度(classical measure))にマイナスのインパクトをもたらすことになる。

コスト削減の圧力が高まる中で、特に先端的な段階にある製造業者にとって 300 mm の生産性を押し上げるニーズが急速に増大していくことになる。しかし、経済情勢の悪化は課題をもたらし、設備投資を抑制してきた。2001 年版ウェー八直径世代ロードマップ(表 2a、2bを参照、さらに詳細はフロントエンドプロセスの章に)では、2001 年初めに 300 mm 能力の立上げで意見が一致している。また、現ロードマップでは、次の 450 mm 径へ 1.5 倍ウェーハ・サイズを大きくすることは 2011-1012 年までに必要になるとは期待されていない。しかし、他の生産性を向上させる原動力(リソグラフィおよび設計/プロセスの改善)がスケジュール

通りに実現しなかった場合、生産性の向上として大直径ウェーハの使用を加速するか他の同等の効果のあるプロセス改善をしなければならないだろう。

将来技術の加速/減速の影響、および次のウェーハ世代への転換のタイミングにより、包括的な長期的な工場の生産性および産業経済モデルの開発と適用が必要となる。現在、SEMI(Semiconductor Equipment and Materials Institute:米国半導体装置材料規格委員会)と国際 SEMATECH (Semiconductor Manufacturing Technology Institute:半導体製造技術研究所)が合同でこのような産業経済モデル化 (industry economic modeling: IEM)の作業を後援し、実行している。

# パッケージされたチップの性能

# パッド数とピン数、パッドピッチ、ピン当たりコスト、周波数

シングルチップのより高い機能の要求は、各製品世代に対するトランジスタ数またはビット(メモリセル)数の集積化を要求する。典型的には、チップのトランジスタ数の増加と同じように、入出力信号を集積回路に導入するのに必要なパッドとピン数も増加する(表 3a、3b 参照)。

また、付加的な電源・グランドのチップへの接続は、熱設計の最適化とノイズ低減に必要である。テスト ITWG により提供されたチップパッド数に基づくと、MPU や高性能 ASIC などのロジック製品は ITRS 期間 の間に4 - 6 kパッドになる。MPU 製品は全パッド数がこの期間に約50%増加し、ASIC は最大パッド数が2 倍になると予想される。また、これらの2タイプの製品は電源 / グランドパッドの割合が本質的に異なっている。 典型的は MPU 製品においては、パッド数の1 / 3が入出力信号であり、2 / 3が電源・グランドである。 言い換えれば、入出力パッド1ケに対して、2ケの電源・グランドパッドを持っている。一方、典型的な高性能 ASIC は、入出力パッド1ケに対して、1ケの電源・グランドパッドを持っている。

表 3a パッケージされたチップの性能:パッド数とピン数(短期)

| 1x 3a 7                                                              |              | 10/27 77  | 07 III 10 . 7 | () PAXCL  | XX ( \\ \tau_1) |           |           |

|----------------------------------------------------------------------|--------------|-----------|---------------|-----------|-----------------|-----------|-----------|

| 製造年                                                                  | 2003         | 2004      | 2005          | 2006      | 2007            | 2008      | 2009      |

| 技術ノード                                                                |              | hp90      |               |           | hp65            |           |           |

| DRAM ½ Pitch (nm)                                                    | 100          | 90        | 80            | 70        | 65              | 57        | 50        |

| MPU/ASIC Metal 1 (M1) ½<br>Pitch (nm)                                | 120          | 107       | 95            | 85        | 76              | 67        | 60        |

| MPU/ASIC ½ Pitch (nm) (Uncontacted Poly)                             | 107          | 90        | 80            | 70        | 65              | 57        | 50        |

| MPU Printed Gate Length (nm) ††                                      | 65           | 53        | 45            | 40        | 35              | 32        | 28        |

| MPU Physical Gate Length (nm)                                        | 45           | 37        | 32            | 28        | 25              | 22        | 20        |

| チップの最大 I/O 数 (Number of )                                            | Total Chip P | ads)      |               |           |                 |           |           |

| Total pads—MPU                                                       | 3,072        | 3,072     | 3,072         | 3,072     | 3,072           | 3,328     | 3,584     |

| Signal I/O—MPU (1/3 of total pads)                                   | 1,024        | 1,024     | 1,024         | 1,024     | 1,024           | 1,109     | 1,195     |

| Power and ground pads—MPU (2/3 of total pads)                        | 2,048        | 2,048     | 2,048         | 2,048     | 2,048           | 2,219     | 2,389     |

| Total pads—ASIC high-<br>performance                                 | 3,400        | 3,600     | 4,000         | 4,200     | 4,400           | 4,600     | 4,800     |

| Signal I/O pads—ASIC high-<br>performance                            | 1,700        | 1,800     | 2,000         | 2,100     | 2,200           | 2,300     | 2,400     |

| Power and ground pads—<br>ASIC high-performance (½ of<br>total pads) | 1,700        | 1,800     | 2,000         | 2,100     | 2,200           | 2,300     | 2,400     |

| 最大パッケージ端子数 [1]                                                       |              |           |               |           |                 |           |           |

| Microprocessor/controller, cost-performance                          | 500-1,452    | 500-1,600 | 550–1,760     | 550–1,936 | 600–2,140       | 660–2,354 | 720–2,568 |

| Microprocessor/controller, high-performance                          | 1,452        | 1,600     | 1,760         | 1,936     | 2,140           | 2,354     | 2,568     |

| ASIC (high-performance)                                              | 2,400        | 3,000     | 3,400         | 3,800     | 4,000           | 4,400     | 4,600     |

#### 表 3a、3bの留意点

- [1] 端子数は、PWB 技術とシステムコストによって狭ピッチ格子接続が使用される幾つかの応用分野によって限られる。

- ・結果として、最多ピン数用途は、より大きなピッチとより大きなパッケージサイズを使用する。

- ・信号ピン比率の関係は用途に依存し、2:1から1:4へと予期された範囲内で大きく変化する。

| 製造年                                                                | 2010      | 2012      | 2013       | 2015       | 2016       | 2018       |  |  |  |  |  |

|--------------------------------------------------------------------|-----------|-----------|------------|------------|------------|------------|--|--|--|--|--|

| 技術ノード                                                              | hp45      |           | hp32       |            | hp22       |            |  |  |  |  |  |

| DRAM ½ Pitch (nm)                                                  | 45        | 35        | 32         | 25         | 22         | 18         |  |  |  |  |  |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                 | 54        | 42        | 38         | 30         | 27         | 21         |  |  |  |  |  |

| MPU/ASIC ½ Pitch (nm) (Un-contacted Poly)                          | 45        | 35        | 32         | 25         | 22         | 18         |  |  |  |  |  |

| MPU Printed Gate Length (nm) ††                                    | 25        | 20        | 18         | 14         | 13         | 10         |  |  |  |  |  |

| MPU Physical Gate Length (nm)                                      | 18        | 14        | 13         | 10         | 9          | 7          |  |  |  |  |  |

| チップの最大 I/O 数 (Number of Total Chip Pads)                           |           |           |            |            |            |            |  |  |  |  |  |

| Total pads- MPU                                                    | 3,840     | 4,096     | 4,224      | 4,352      | 4,416      | 4,544      |  |  |  |  |  |

| Signal I/O- MPU (1/3 of total pads)                                | 1,280     | 1,365     | 1,408      | 1,451      | 1,472      | 1,515      |  |  |  |  |  |

| Power and ground pads— MPU (2/3 of total pads)                     | 2,560     | 2,731     | 2,816      | 2,901      | 2,944      | 3,029      |  |  |  |  |  |

| Total pads- ASIC high-performance                                  | 4,800     | 5,200     | 5,400      | 5,800      | 6,000      | 6,400      |  |  |  |  |  |

| Signal I/O pads- ASIC high-<br>performance                         | 2,400     | 2,600     | 2,700      | 2,900      | 3,000      | 3,200      |  |  |  |  |  |

| Power and ground pads— ASIC high-<br>performance (½ of total pads) | 2,400     | 2,600     | 2,700      | 2,900      | 3,000      | 3,200      |  |  |  |  |  |

| 最大パッケージ端子数 [1]                                                     |           |           |            |            |            |            |  |  |  |  |  |

| Microprocessor/controller, cost-<br>performance                    | 780–2,782 | 936–3,338 | 1014–3,616 | 1217-4,340 | 1318–4,702 | 1521–5,426 |  |  |  |  |  |

| Microprocessor/controller, high-<br>performance                    | 2,782     | 3,338     | 3,616      | 4,340      | 4,702      | 5,426      |  |  |  |  |  |

| ASIC (high-performance)                                            | 4,009     | 4,810     | 5,335      | 6,402      | 7,042      | 8,450      |  |  |  |  |  |

表 3b パッケージされたチップの性能: パッド数とピン数(長期)

A&P ITWG から提供されたパッケージピン数(表 3a、3b)とピン当たりコスト(表 4a、4b)は、将来的な製造経済学への挑戦を指摘している。チップ当たりのトランジスタ数の増加に基づくと、パッケージピン数(ボール数)は年率約10%で増加し、ピン当たりコストは年率5%で減少すると予想される。これらのトレンドは、パッケージング技術のサプライヤにとって、低コスト解を提供する事をより困難にしている。何故ならば、パッケージング全般における平均コストは年率5%で増加するからである(0.95cost/pin×1.10pins/year = 1.05cost/year)。

非常に競争の激しいコンシューマ電子機器環境においては、パソコンや携帯電話のような大規模なハイテク製品の価格は、現状維持か、減少傾向となる。これらのハイテク製品は典型的には2年毎に2倍の性能を提供している。これは最先端半導体製造メーカの最終用途市場環境であり、関数(ビット、トランジスタ)当たりコストの年率30%またはそれ以上の低減の ITRS 経済的要求に従う、基本的な経済的牽引車である(同じ価格で、2年毎に $2\times$ チップ当たりの関数性 = 29%/year)。

もし、将来の半導体素子製品の価格を維持もしくは低下することを目標とし、また、平均のピン当たりコストが5%しか削減出来ない時に、ユニット当たりの平均ピン数が10%増加するとした場合、次のようになる。

- 1.全コストに占める平均パッケージングコストの割合は、15年間のロードマップ期間に倍増する。

- 2. 最終結果は総収益マージンの大幅な減少と研究開発/工場生産能力への投資能力の制限となる。

この結論が、システム・オン・チップ(System-on-Chip: SoC)への機能統合ならびにマルチチップ・モジュールやバンプ型チップ・オン・ボード(Chip-on-Board: COB)やその他の創造的な解決策の使用により、全体のシステムのピン数要求を低減させる業界傾向の原動力の1つとなっている。

機能当たりのコストを指数的に削減しながら機能を増加するニーズに加えて、高性能低コスト型製品への市場の要求も存在する。消費者の要求を満たすために  $1.5 \sim 2$  年毎にチップ当たりの機能が倍増するというムーアの法則が予測するように、ますます高スピードで電気信号を処理したいという要求も存在する。 MPU の場合、今までプロセッサの命令数/秒も  $1.5 \sim 2$  年ごとに倍増している。MPU 製品について、百万命令/秒 (millions of instructions per second: MIPs)の単位で測定される処理能力の増加は、「本質の技術性能」(クロック周波数)×「アーキテクチャ性能」(クロック・サイクル毎の命令)の組合せで達成される。ますます高くなる動作周波数へのニーズは、新規のプロセス、設計、パッケージング技術の開発を継続的に要求していく。

最大オン・チップ (on-chip) 周波数と最大チップ・ツー・ボード (chip-to-board) 周波数の動向を予測するため、設計 ITWG およびアセンブリ&パッケージ ITWG から提供された行項目を含む表 4c、4d には、上記の考慮が反映されている。各製品世代で入手可能な最大周波数は、固有トランジスタ性能 (オン・チップ、ローカル・クロック) に直接関係している。ライン・ツー・ライン (line-to-line) およびライン・ツー・サブストレート (line-to-substrate) の容量結合がもたらす信号伝播遅延の劣化により、チップを横切って伝播する信号の周波数とこの「ローカル」 周波数との差が拡大している。他の信号劣化はワイヤ・ボンドおよびパッケージ・リードのインダクタンスに関連している。パッケージがもたらす寄生効果を排除する唯一の実行可能な手段は、チップの直接取り付けであろう。チップ全体の信号とパワーの分布を最適化するため、配線層数が今後も増加することが予測される。配線のダウン・スケーリングも継続するので、銅配線 (低抵抗率) および低誘電率  $(\kappa \sim 2-3)$  を持つ様々な層間絶縁材料が、チップ製造工程において幅広く採用されるだろう。チップ・ツー・ボード動作周波数 (47) ・チップ)を上げるために、多重化手法も使用されるだろう。

表 4a 性能およびパッケージ・チップ:パッド、コスト (短期)

| 製造年                                          | 2003 | 2004 | 2005 | 2006 | 2007 | 2008 | 2009 |

|----------------------------------------------|------|------|------|------|------|------|------|

| 技術ノード                                        |      | hp90 |      |      | hp65 |      |      |

| DRAM ½ Pitch (nm)                            | 100  | 90   | 80   | 70   | 65   | 57   | 50   |

| MPU/ASIC Metal 1 (M1) ½<br>Pitch (nm)        | 120  | 107  | 95   | 85   | 76   | 67   | 60   |

| MPU/ASIC ½ Pitch (nm)<br>(Un-contacted Poly) | 107  | 90   | 80   | 70   | 65   | 57   | 50   |

| MPU Printed Gate Length (nm)                 | 65   | 53   | 45   | 40   | 35   | 32   | 28   |

| MPU Physical Gate Length (nm)                | 45   | 37   | 32   | 28   | 25   | 22   | 20   |

| チップ・パッド・ピッチ (micron)                         |      |      |      |      |      |      |      |

| Pad pitch—ball bond                          | 40   | 35   | 30   | 25   | 25   | 20   | 20   |

| Pad pitch—wedge bond                         | 30   | 25   | 20   | 20   | 20   | 20   | 20   |

| Pad pitch—wedge bond                         | 30   | 25   | 20   | 20   | 20   | 20   | 20   |

| Pad Pitch—area array flip-chip<br>(cost-performance, high-<br>performance) | 150       | 150      | 130      | 130      | 120      | 110      | 100     |

|----------------------------------------------------------------------------|-----------|----------|----------|----------|----------|----------|---------|

| Pad Pitch—peripheral flip-chip<br>(handheld, low-cost, harsh)              | 60        | 60       | 40       | 40       | 30       | 30       | 20      |

| ピン当たりコスト                                                                   |           |          |          |          |          |          |         |

| Package cost (cents/pin)<br>(cost-performance)—<br>minimum-maximum         | .75–1.30  | .71–1.24 | .67–1.17 | .64–1.11 | .61–1.05 | .58–1.00 | .55–.96 |

| Package cost (cents/pin)<br>(Memory)—minimum–<br>maximum                   | 0.30-0.56 | 0.29–.53 | .27–.50  | ,26–.48  | ,25–.45  | .23–.43  | .22–.41 |

# 表 4b 性能およびパッケージ·チップ:パッド、コスト(長期)

|                                                                     |           | ı         | 1         | ı         | 1         | 1         |

|---------------------------------------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|

| 製造年                                                                 | 2010      | 2012      | 2013      | 2015      | 2016      | 2018      |

| 技術ノード                                                               | hp45      |           | hp32      |           | hp22      |           |

| DRAM ½ Pitch (nm)                                                   | 45        | 35        | 32        | 25        | 22        | 18        |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                  | 54        | 42        | 38        | 30        | 27        | 21        |

| MPU/ASIC ½ Pitch (nm) (Un-contacted Poly)                           | 45        | 35        | 32        | 25        | 22        | 18        |

| MPU Printed Gate Length (nm) ††                                     | 25        | 20        | 18        | 14        | 13        | 10        |

| MPU Physical Gate Length (nm)                                       | 18        | 14        | 13        | 10        | 9         | 7         |

| チップ・パッド・ピッチ (micron)                                                |           |           |           |           |           |           |

| Pad pitch—ball bond                                                 | 20        | 20        | 20        | 20        | 20        | 20        |

| Pad Pitch—wedge bond                                                | 20        | 20        | 20        | 20        | 20        | 20        |

| Pad Pitch—area array flip-chip (cost-performance, high-performance) | 100       | 90        | 90        | 80        | 80        | 70        |

| Pad Pitch—peripheral flip-chip (handheld, low-cost, harsh)          | 20        | 20        | 20        | 15        | 15        | 15        |

| ピン当たりコスト                                                            |           |           |           |           |           |           |

| Package cost (cents/pin) (cost-performance)—<br>minimum-maximum     | 0.52-0.94 | 0.5–.86   | 0.5–.77   | 0.5-0.69  | 0.5-0.65  | 0.5-0.59  |

| Package cost (cents/pin) (Memory)— minimum-<br>maximum              | .22–.41   | 0.22-0.36 | 0.22–0.35 | 0.22-0.31 | 0.22-0.29 | 0.22-0.27 |

表 4c 性能およびパッケージ·チップ: 周波数、オン·チップ配線層数 (短期)

| 製造年                                       | 2003 | 2004 | 2005 | 2006 | 2007 | 2008 | 2009 |

|-------------------------------------------|------|------|------|------|------|------|------|

| 技術ノード                                     |      | hp90 |      |      | hp65 |      |      |

| DRAM ½ Pitch (nm)                         | 100  | 90   | 80   | 70   | 65   | 57   | 50   |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)        | 120  | 107  | 95   | 85   | 76   | 67   | 60   |

| MPU/ASIC ½ Pitch (nm) (Un-contacted Poly) | 107  | 90   | 80   | 70   | 65   | 57   | 50   |

| MPU Printed Gate Length (nm) ††           | 65   | 53   | 45   | 40   | 35   | 32   | 28   |

| MPU Physical Gate Length (nm)             | 45   | 37   | 32   | 28   | 25   | 22   | 20   |

| チップ周波数 (MHz)                              |      |      |      |      |      |      |      |

| On-chip local clock                                                           | 2,976 | 4,171 | 5,204 | 6,783 | 9,285 | 10,972 | 12,369 |

|-------------------------------------------------------------------------------|-------|-------|-------|-------|-------|--------|--------|

| Chip-to-board (off-chip) speed<br>(high-performance, for peripheral buses)[1] | 2,000 | 2,500 | 3,125 | 3,906 | 4,883 | 6,103  | 7,629  |

| Maximum number wiring levels—maximum                                          | 13    | 14    | 15    | 15    | 15    | 16     | 16     |

| Maximum number wiring levels—minimum                                          | 9     | 10    | 11    | 11    | 11    | 12     | 12     |

表 4d 性能およびパッケージ・チップ: 周波数、オン・チップ配線層数 (長期)

| 製造年                                                                              | 2010   | 2012   | 2013   | 2015   | 2016   | 2018   |

|----------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|

| 技術ノード                                                                            | hp45   |        | hp32   |        | hp22   |        |

| DRAM ½ Pitch (nm)                                                                | 45     | 35     | 32     | 25     | 22     | 18     |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                               | 54     | 42     | 38     | 30     | 27     | 21     |

| MPU/ASIC ½ Pitch (nm) (Uncontacted Poly)                                         | 45     | 35     | 32     | 25     | 22     | 18     |

| MPU Printed Gate Length (nm) ††                                                  | 25     | 20     | 18     | 14     | 13     | 10     |

| MPU Physical Gate Length (nm)                                                    | 18     | 14     | 13     | 10     | 9      | 7      |

| チップ周波数 (MHz)                                                                     |        |        |        |        |        |        |

| On-chip local clock                                                              | 15,079 | 20,065 | 22,980 | 33,403 | 39,683 | 53,207 |

| Chip-to-board (off-chip) speed<br>(high-performance, for peripheral<br>buses)[1] | 9,536  | 14,901 | 18,626 | 29,103 | 36,379 | 56,843 |

| Maximum number wiring levels— maximum                                            | 16     | 16     | 16     | 17     | 18     | 18     |

| Maximum number wiring levels—minimum                                             | 12     | 12     | 12     | 13     | 14     | 14     |

### 表 4c、4d の注記

- [1] 多数の低速ピンと組み合わせて使用される少数の高速ピンに対して、オフ・チップ周波数が増加すると予測される。 [2] 2001 年、高速シリアル通信トランシーバ素子のチップー基板周波数は、CMOS 使用で 3.125GHz、SiGe 使用で 10GHz に達している。 2002 年には、CMOS 使用で 10GHz のトランシーバが作製されるだろう。 40GHz の SiGe 素子も 2003 年には期待される。 より広いバス幅を持つ高レベル集積回路の動向は、テストの章の高周波シリアル通信の節で説明する。

- [3] 配線層数の最小値は接続メタル層数を表し、最大値は更にパワー、グランド、信号調整、受動素子(例えば、キャパシタ)集積などの追加配線層数を含んでいる。

### 電気的な欠陥密度

DRAM、MPU、ASIC の電気的欠陥の密度に関する(量産の年に 83~89.5 %のチップ歩留を達成するのに必要な)最新目標を表 5a、5bに示す。DRAM とマイクロプロセッサについて表 1 で報告したように、最新チップ寸法モデルに基づき異なるチップ寸法を考慮して、許容可能な欠陥数を計算している。その上、図表内のデータは生産ライフサイクルの内量産レベルだけが報告されている。歩留向上についての章に載せた式を使用して、同一テクノロジ・ノードでの異なるチップ寸法における他の欠陥密度を計算することが出来る。常に増加しているプロセス複雑性の指標として、ロジック・デバイス用マスク層の概数を載せている。

| Year of Production                                                                                  | 2003  | 2004  | 2005  | 2006  | 2007  | 2008  | 2009  |

|-----------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|

| Technology Node                                                                                     |       | hp90  |       |       | hp65  |       |       |

| DRAM ½ Pitch (nm)                                                                                   | 100   | 90    | 80    | 70    | 65    | 57    | 50    |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                                                  | 120   | 107   | 95    | 85    | 76    | 67    | 60    |

| MPU/ASIC ½ Pitch (nm) (Un-contacted Poly)                                                           | 107   | 90    | 80    | 70    | 65    | 57    | 50    |

| MPU Printed Gate Length (nm) ††                                                                     | 65    | 53    | 45    | 40    | 35    | 32    | 28    |

| MPU Physical Gate Length (nm)                                                                       | 45    | 37    | 32    | 28    | 25    | 22    | 20    |

| DRAM Random Defect D <sub>0</sub> at production chip size and 89.5% yield (faults/m²) §             | 2,216 | 2,791 | 3,751 | 2,532 | 3,190 | 2,345 | 2,954 |

| MPU Random Defect D <sub>0</sub> at production chip size and 83% yield (faults/ m <sup>2</sup> ) §§ | 1,395 | 1,395 | 1,395 | 1,395 | 1,395 | 1,395 | 1,395 |

| # Mask Levels—MPU                                                                                   | 29    | 31    | 33    | 33    | 33    | 35    | 35    |

| # Mask Levels—DRAM                                                                                  | 24    | 24    | 24    | 24    | 24    | 24    | 24    |

表 5a 電気的な欠陥—短期

表5b 電気的な欠陥―長期

| Year of Production                                                                                    | 2010  | 2012  | 2013  | 2015  | 2016  | 2018  |

|-------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|

| Technology Node                                                                                       | hp45  |       | hp32  |       | hp22  |       |

| DRAM ½ Pitch (nm)                                                                                     | 45    | 35    | 32    | 25    | 22    | 18    |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                                                    | 54    | 42    | 38    | 30    | 27    | 21    |

| MPU/ASIC ½ Pitch (nm) (Un-contacted Poly)                                                             | 45    | 35    | 32    | 25    | 22    | 18    |

| MPU Printed Gate Length (nm) ††                                                                       | 25    | 20    | 18    | 14    | 13    | 10    |

| MPU Physical Gate Length (nm)                                                                         | 18    | 14    | 13    | 10    | 9     | 7     |

| DRAM Random Defect D <sub>0</sub> at production chip size and 83% yield (faults/ m <sup>2</sup> ) §   | 3,722 | 2,954 | 3,722 | 2,954 | 2,233 | 3,545 |

| MPU Random Defect D <sub>0</sub> at production chip size and 89.5% yield (faults/ m <sup>2</sup> ) §§ | 1,395 | 1,395 | 1,395 | 1,395 | 1,395 | 1,395 |

| # Mask Levels—MPU                                                                                     | 35    | 35    | 35    | 37    | 39    | 39    |

| # Mask Levels—DRAM                                                                                    | 26    | 26    | 26    | 26    | 26    | 26    |

### 表 5aと5bの注記:

# D<sub>0</sub>—欠陥密度

§DRAM モデル・セル・ファクタ(設計/プロセスの改善目標)を以下に示す。

1999—2004/8×; 2005/7.5x; 2006-2007/7x; 2008-2015/6x; 2016-2018/5x. "6"DRAMセル設計改善ファクター  $\{a\}$ の 2003年から 2008年への 5年の遅れのために"ムーアの法則"でビット/チップが 1.5年ごと 2x から 2年ごと 2x に、更に減速することを余儀なくされた。

下記を除いて、DRAM 量産世代は、間に  $2\times E'$ ット/チップの暫定的な世代があるが、4 年ごとに  $4\times E'$ ット/チップの割合で一般的に増加する。

- 1. 導入フェーズにおいて、16G ビット中間世代の後、導入レートは 4×/6 年(2×/3 年)である。

- 2. 量産フェーズにおいて、1G ビット世代の後、導入レートは 4×/5 年(2×/2~3 年)である。

もともとの 2001ITRSの世代間チップ寸法の成長率は、導入時に 572mm<sup>2</sup>フィールド(field)あたり 1 チップおよび生産時に 572mm<sup>2</sup>フィールドあたり 2 チップが入ることを目標にしている。セル・エリア・ファクター削減の遅れのために、導

入時のチップ寸法は増加したが、新しい 704 mm² 最大許容描画領域のお陰で、導入時のチップはチップ当たりのビット数を 2 年毎に 2 倍にすることが 16 Gビット世代 (660 mm²/2007)まで可能となった。「ムーアの法則」の遅れで、導入時の DRAM モデルのビット / チップが平均 2.5 年ごと 2xになったことにより、導入時の DRAM が元々の 572 mm²以下の許容できる寸法に 2007 年以降収まるようになった。世代内チップ寸法シュリンクモデルは、セル・ファクタ縮小の中間でのテクノロジ・ノードごとに  $0.5\times$ であり、最終的には (5 年から 6 年に渡って) 導入時の DRAM はシュリンクを行なって量産時のチップ寸法目標である 140 mm²以下になる。

§§ MPU チップ・サイズ・モデル: コスト重視 MPU と高性能 MPU の世代間チップ寸法成長率は、2018 年まで一定とされている  $(280 \, \text{mm}^2 / \, \text{コスト重視 MPU 導入時; } 140 \, \text{mm}^2 / \, \text{コスト重視 MPU 量産時; } 310 \, \text{mm}^2 / \, \text{高性能 MPU 量産時)。} MPUのチップ寸法一定のモデルはテクノロジ・ノード・サイクルごとのオンチップ機能の倍増により可能となる。世代内チップ寸法シュリンク小モデルは、<math>2001$  年まで 2 年テクノロジ・ノードごとに  $0.5 \times \text{であり}$ 、今や 2003 年以降は 3 年 テクノロジ・ノードごとに  $0.5 \times \text{である}$ 。

用語 - 導入、量産、世代間、世代内については、用語集を参照して頂きたい。

# 電源と消費電力

いくつかの要因(消費電力の低下、トランジスタチャネル長の縮小、ゲート誘電体信頼性の向上)が電源電圧の低減(表 6a、6b参照)を推し進めている。表 6a、6bに示すように、現在、電源電圧の値は範囲で与えられている。

特定の  $V_{dd}$ 値の選択は、1個の IC について速度と電力を同時に最適化する解析の一部として続けられており、各製品世代の使用可能電源電圧の範囲をもたらしている。高性能プロセッサーで 0.5V  $V_{dd}$  値は 2018 年までには達成されないだろう(2001 年版ITRSでは 2001 年で達成されると期待されていたが)。現在の最低目標値は低消費電力応用製品で 2016年に 0.4V となっており、(これは 2001年版 IRTS の 0.6V目標より低い値になっている。

最大電力傾向(例、MPU用)は3つのカテゴリで提示される。

- 1) 高性能デスクトップ・アプリケーション、パッケージのヒート・シンクを許容。

- 2) コスト重視型、最高性能の経済的な電力管理が最も重要。

- 3) 携帯電池運用(今や、アセンブリー・パッケージのTWGで「厳しい: Harsh」環境と名づけられている。)

全てのカテゴリで、低電源電圧の使用にもかかわらず、全体の電力消費量は増加し続けている。高チップ使用周波数、配線全体の高容量と高抵抗、および指数的増加しかつスケール・アップするチップ上トランジスタのゲート・リーク(漏れ)の増大などが電力消費量の増加を推し進めている。

| Year of Production                            | 2003 | 2004 | 2005 | 2006 | 2007 | 2008 | 2009 |

|-----------------------------------------------|------|------|------|------|------|------|------|

| Technology Node                               |      | hp90 |      |      | hp65 |      |      |

| DRAM ½ Pitch (nm)                             | 100  | 90   | 80   | 70   | 65   | 57   | 50   |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)            | 120  | 107  | 95   | 85   | 76   | 67   | 60   |

| MPU/ASIC ½ Pitch (nm) (Un-<br>contacted Poly) | 107  | 90   | 80   | 70   | 65   | 57   | 50   |

| MPU Printed Gate Length (nm) ††               | 65   | 53   | 45   | 40   | 35   | 32   | 28   |

表 6a 電源と消費電力—短期

| 2 |  |

|---|--|

|   |  |

|   |  |

| MPU Physical Gate Length (nm)                                           | 45  | 37  | 32  | 28  | 25  | 22  | 20  |

|-------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Power Supply Voltage (V)                                                |     |     |     |     |     |     |     |

| V <sub>dd</sub> (high-performance)                                      | 1.2 | 1.2 | 1.1 | 1.1 | 1.1 | 1.0 | 1.0 |

| V <sub>dd</sub> (Low Operating Power, high V <sub>dd</sub> transistors) | 1.0 | 0.9 | 0.9 | 0.9 | 0.8 | 0.8 | 0.8 |

| Allowable Maximum Power [1]                                             |     |     |     |     |     |     |     |

| High-performance with heatsink (W)                                      | 149 | 158 | 167 | 180 | 189 | 200 | 210 |

| Cost-performance (W)                                                    | 80  | 84  | 91  | 98  | 104 | 109 | 114 |

| Battery (W)—(low-cost/hand-held)                                        | 2.1 | 2.2 | 2.3 | 2.4 | 2.5 | 2.6 | 2.7 |

表 6b 電源と消費電力—長期

| Year of Production                              | 2010 | 2012 | 2013 | 2015 | 2016 | 2018 |

|-------------------------------------------------|------|------|------|------|------|------|

| Technology Node                                 | hp45 |      | hp32 |      | hp22 |      |

| DRAM ½ Pitch (nm)                               | 45   | 35   | 32   | 25   | 22   | 18   |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)              | 54   | 42   | 38   | 30   | 27   | 21   |

| MPU/ASIC ½ Pitch (nm) (Un-contacted Poly)       | 45   | 35   | 32   | 25   | 22   | 18   |

| MPU Printed Gate Length (nm) ††                 | 25   | 20   | 18   | 14   | 13   | 10   |

| MPU Physical Gate Length (nm)                   | 18   | 14   | 13   | 10   | 9    | 7    |

| Power Supply Voltage (V)                        |      |      |      |      |      |      |

| Vdd (high-performance)                          | 1.0  | 0.9  | 0.9  | 0.8  | 0.8  | 0.7  |

| Vdd (Low Operating Power, high Vdd transistors) | 0.7  | 0.7  | 0.6  | 0.6  | 0.5  | 0.5  |

| Allowable Maximum Power [1]                     |      |      |      |      |      |      |

| High-performance with heatsink (W)              | 218  | 240  | 251  | 270  | 288  | 300  |

| Cost-performance (W)                            | 120  | 131  | 138  | 148  | 158  | 168  |

| Battery (W)—(hand-held)                         | 2.8  | 3.0  | 3.0  | 3.0  | 3.0  | 3.0  |

### 表 6aと6bの注記:

[1] 電源は実装よりもシステム・レベルの冷却とテスト制約により制限を受ける。

### コスト

表 7a と 7bはコストの傾向を示している。機能あたりのコストを年間に平均 25~30%削減が可能なことは 半導体産業に特有な特徴であり、定価格または低下した価格環境の中で 1.5~2 年ごとにチップ上機能の 倍増を提供しつづけることは、市場圧力の直接的な結果である。このコスト削減圧力に対応するため、研究 開発部門と製造部門では多額の設備投資を継続的に実施していかなければならない。工場あたりの投資 額ベースでさえも、製造部門への設備投資額は上昇の一途を辿っている。しかし、歴史的に半導体産業は、 チップ寸法とコストを増加させずに、または適度な増加によって、1.5~2 年ごとにチップあたりの機能倍増を 提供しており、シリコンの cm² あたりではおおよそ一定コストとなっている。技術面の性能と経済面での効果 が半導体産業の成長を支えてきた基本エンジンであった。

しかし、今日の競争的市場環境の中にいる顧客は僅かなコスト増加にさえも抵抗を示し、チップとユニットコストを制御するために、今までチップあたりの機能倍増のスピード(ムーアの法則)にも圧力を加えている。 そのため、半導体メーカは、半導体産業の成長を今まで担ってきた、同じような機能あたりのコスト削減必要 条件を提供する新しいモデルを捜し求めなければならなくなっている。そのため、1999 年版 ITRS では所望の削減を達成する新しいモデルが提案されている。チップあたり定コストおよび平均販売価格(average selling price: ASP)で2年ごとに機能倍増を顧客に提供している。2001と2003年版 ITRS はそのモデルを使って、一機能(ビット、トランジスター等)当たり29%のコスト削減となる。今まで(1999年以前は)、ユニットあたりのコストを1.4×増の割合で3年ごとにチップあたりの機能4倍増を達成している。

2003 年版ITRSの DRAM および MPU のコスト・モデルは、半導体産業の経済性の原動力として、機能生産性あたりのコストの 29%削減レートへのニーズを使い続けている。そのため、DRAM およびマイクロプロセッサについて手ごろなコスト/ビットやコスト/トランジスタの世代内傾向を設定するために、この中心的な機能あたりのコストの傾向を使用してきている。今までの傾向から推測すると、4G ビット DRAM について、「初期の」手ごろな値段のコスト/ビットが 2003 年には約 10.5 マイクロセント(microcent) であることが示されている。加えて、その今までの傾向は、1 DRAM 世代内では年間 45%のコスト/ビット削減が期待されるべきであることを示している。1 これに対応して、マイクロプロセッサについて公表データを使って行った解析は同様な結果をもたらしている。2 結果として、MPU モデルにも、同一世代内で 45%の削減レート値とともに、世代間で手ごろなコスト/トランジスタの削減目標値 29%/年が使用されている。

2003 年版ITRSは元々の 2001 年版MPUチップ寸法モデルを使っている。設計 ITWG は 2001 年版ITRSで当時のデータに基づいて MPU モデルをアップデートしている。当時のデータは、ロジック・トランジスタの寸法がリソグラフィのレート(テクノロジ・ノードごとに 0.7×リニア縮小および 0.5×エリヤ縮小)の割合でしか改善していないことを示している。そのため、MPU チップ寸法を一定に保つために、トランジスタの数は、テクノロジ・ノードごとにしか倍増していない。テクノロジ・ノードのレートは 2001 年以降に 3 年サイクルに戻ると予測されており、従って、2001 年以降 MPU チップあたりのトランジスタ数は 3 年ごとにしか倍増しないことになる。

DRAM メモリ・ビット・セル設計の改善スピードも、2003 年版ITRS・DRAMチップ寸法モデル目標を反映して、スローダウンしている。「6」の設計ファクター、即ち「8」ファクターに対し 25%の改善は 2003 年に導入されると期待されていたが、今や 5 年遅れの 2008 年となった。更に「4」の設計ファクター、即ち「6」ファクターに対して 33%の改善は、2003 年版ITRSでは「5」に変更され、2011 年から 2016 年に遅れた。結果的には、セル・エリア効率の目標が 63%に引き上げられ、将来チップあたりのビットのスピードも低下して  $2 \times /2$  年から、 $2 \times /2.5$ -3.0 年になる。チップ寸法を  $140 \text{mm}^2$ 以下の一定チップ寸法に保つために、2003 年ITRS・DRAMチップ寸法モデルへのこれらの調整が必要である。

DRAM と MPU におけるチップあたりの機能のレート低下を補うために、チップ・レベル・アーキテクチャ、システム・レベル・アーキテクチャ、設計などの等化生産性スケーリングから得られる利益から、別の生産性向上策を見出す方向への圧力がますます高まるだろう。

<sup>&</sup>lt;sup>7</sup> McClean, William J. 編集、 1994年 中期: IC 産業のステータスと予測、 Scottsdale: Integrated Circuit Engineering Corporation、 1994., McClean, William J. 編集、 1995年 中期: IC 産業のステータスと予測、 Scottsdale: Integrated Circuit Engineering Corporation, 1995.

<sup>&</sup>lt;sup>2</sup> a) Dataquest Incorporated、x86 マーケット: 詳細な予測、仮定、傾向、 MCRO-WW-MT-9501. San Jose: Dataquest Incorporated、1995/01/16.

b) Port, Otis、Reinhardt, Andy、McWilliams, Gary、Brull, Steven V. 「シリコン時代?今夜明けを迎えている」図表 1、Business Week、1996/12/09、148–152.

かりに将来チップ上機能の増加レートが低下したとしても、機能/チップの量はまだ指数的に成長している。機能/チップの数が増加し続けるので、最終製品のテストはますます困難になり、従って、コストが高くなっている。これは、テスタのコスト上昇に反映されている。たとえテスタ・ピンあたりのコストが増加すると予測されており(表 7a、7b)、ピン数も増加する(表 4a、4b)。それゆえ、組込みセルフ・テスト(Built-in Self Test: BIST)手法およびテスト容易化設計(Design-For- Testability: DFT)手法の実現加速へのニーズは、2003年版半導体国際テクノロジ・ロードマップのタイムフレーム内で引き続いて存在する。詳しい説明はテストの章で述べる。

表 7a コスト-短期

| Year of Production                                                                              | 2003 | 2004 | 2005 | 2006 | 2007 | 2008 | 2009 |

|-------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|

| Technology Node                                                                                 |      | hp90 |      |      | hp65 |      |      |

| DRAM ½ Pitch (nm)                                                                               | 100  | 90   | 80   | 70   | 65   | 57   | 50   |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                                              | 120  | 107  | 95   | 85   | 76   | 67   | 60   |

| MPU/ASIC ½ Pitch (nm) (Un-contacted Poly)                                                       | 107  | 90   | 80   | 70   | 65   | 57   | 50   |

| MPU Printed Gate Length (nm) ††                                                                 | 65   | 53   | 45   | 40   | 35   | 32   | 28   |

| MPU Physical Gate Length (nm)                                                                   | 45   | 37   | 32   | 28   | 25   | 22   | 20   |

| Affordable Cost per Function ++                                                                 |      |      |      |      |      |      |      |

| DRAM cost/bit at (packaged microcents) at samples/introduction                                  | 10.5 | 7.4  | 5.3  | 3.7  | 2.6  | 1.9  | 1.3  |

| DRAM cost/bit at (packaged microcents) at production §                                          | 3.8  | 2.7  | 1.9  | 1.4  | 0.96 | 0.7  | 0.5  |

| Cost-performance MPU (microcents/transistor)<br>(including on-chip SRAM) at introduction §§     | 88   | 62   | 44   | 31   | 22   | 15.6 | 11.0 |

| Cost-performance MPU (microcents/transistor)<br>(including on-chip SRAM) at production §§       | 53   | 38   | 27   | 19   | 13.3 | 9.4  | 6.7  |

| High-performance MPU (microcents/transistor)<br>(including on-chip SRAM) at production §§       | 49   | 34   | 24   | 17   | 12   | 8.6  | 6.1  |

| Cost-Per-Pin                                                                                    |      |      |      |      |      |      |      |

| Test Cost                                                                                       |      |      |      |      |      |      |      |

| Volume tester cost per high-frequency signal pin<br>(SK/pin)<br>(high-performance ASIC)—maximum | 3    | 3    | 3    | 3    | 3    | 3    | 3    |

| Volume tester cost per high-frequency signal pin<br>(SK/pin)<br>(high-performance ASIC)—minimum | 1    | 1    | 1    | 1    | 1    | 1    | 2    |

図表 7b コスト-長期

| Year of Production                        | 2010 | 2012 | 2013 | 2015 | 2016 | 2018 |

|-------------------------------------------|------|------|------|------|------|------|

| Technology Node                           | hp45 |      | hp32 |      | hp22 |      |

| DRAM ½ Pitch (nm)                         | 45   | 35   | 32   | 25   | 22   | 18   |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)        | 54   | 42   | 38   | 30   | 27   | 21   |

| MPU/ASIC ½ Pitch (nm) (Un-contacted Poly) | 45   | 35   | 32   | 25   | 22   | 18   |

| MPU Printed Gate Length (nm) ††           | 25   | 20   | 18   | 14   | 13   | 10   |

| MPU Physical Gate Length (nm)             | 18   | 14   | 13   | 10   | 9    | 7    |

| Affordable Cost per Function ++           |      |      |      |      |      |      |

| DRAM cost/bit (packaged microcents) at samples/introduction                                     | 0.93  | 0.46 | 0.33 | 0.16 | 0.12  | 0.06  |

|-------------------------------------------------------------------------------------------------|-------|------|------|------|-------|-------|

| DRAM cost/bit (packaged microcents) at production §                                             | 0.34  | 0.17 | 0.12 | 0.06 | 0.042 | 0.021 |

| Cost-performance MPU (microcents/transistor)<br>(including on-chip SRAM) at introduction §§     | 7.78  | 3.89 | 2.75 | 1.38 | 0.97  | 0.49  |

| Cost-performance MPU (microcents/transistor)<br>(including on-chip SRAM) at production §§       | 4.71  | 2.35 | 1.66 | 0.83 | 0.59  | 0.29  |

| High-performance MPU (microcents/transistor) (including on-chip SRAM) at production §§          | 4.305 | 2.15 | 1.52 | 0.76 | 0.54  | 0.27  |

| Cost-Per-Pin                                                                                    |       |      |      |      |       |       |

| Test Cost                                                                                       |       |      |      |      |       |       |

| Volume tester cost per high-frequency signal pin<br>(SK/pin)<br>(high-performance ASIC)—maximum | 4     | 4    | 4    | 4    | 4     | 4     |

| Volume tester cost per high-frequency signal pin<br>(SK/pin)<br>(high-performance ASIC)—minimum | 2     | 2    | 3    | 3    | 4     | 4     |

### 表 7a と 7b の注記:

++荒利マージン(Gross Profit Margins: GPM)を差し引いた、様々な解析レポートから入手できた、平均販売価格 (Average Selling Price: ASP)に基づく機能あたりの許容可能な実装済みユニットのコスト。DRAM 製品には 35% GPM、MPU には 60%GPM を使用。 $0.5\times/2$  年世代間縮小レートモデルを使用。 $0.55\times/4$  年世代内縮小レートモデルを使用。次世代が世代内機能あたりのコストをクロスした時点で DRAM ユニット量がライフサイクルのピークが起こる(一般的に導入後  $7\sim8$ 年)。MPU ユニット量ライフサイクルのピークは一般的に  $4\sim6$ 年後、次世代プロセッサが立上げフェーズに入った時点で起こる(一般的に導入後  $2\sim4$ 年)。

§DRAM モデル・セル・ファクタ(設計/プロセスの改善目標)を以下に示す。

1999-2004/8×:2005/7 . 5 x ; 2006-2007/7×: 2008-2015/6×: 2016-2018/5 x . 「6」のDRAMセル設計改善

ファクター[a]の 2003 年から 2008 年への 5 年の遅れのために、「ムーアの法則」はチップ当たりビット数で 1.5 から 2 年で 2 倍にから、2003 年版 I T R S・D R A M チップ寸法モデルの 2.5 年から 3 年で 2 倍にへになり、2004 年以降は 3 年の D R A M ハーフピッチ・ノード・サイクルに落ち着く。

下記を除いて、DRAM 生産世代は、間に 2×ビット/チップの暫定的な世代があるが、4年ごとに 4×ビット/チップの割合で一般的に増加する。

- 1. 導入フェーズにおいて、16G ビット中間世代の後、導入レートは 4×/5 年(2×/3 年)である。

- 2. 生産フェーズにおいて、1G ビット世代の後、導入レートは 4×/5 年(2×/2~3 年) である。

量産フェーズのDRAMの世代間(InTER-generation)チップ寸法成長率モデル目標は、今やMPUのモデルと同様に  $140 \text{mm}^2$ 以下で一定である。この新しい一定チップ寸法モデル目標により、チップ当たりビット数の「ムーア」の法則DRAMモデルはチップ当たりのビット数が 2 倍になるのに、  $2 \times /2$  年と  $2 \times /3$  年を繰り返して平均  $2 \times /2$  . 5 年に延びた(ORTC表 1 C、dを参照)。加えるに、セル・アレー効率(全チップ面性に対するメモリー・アレー%)は 63%に増加し、このため、量産フェーズの製品チップ寸法が、セル設計改善ファクターの遅れ(上の記述参照)にもかかわらず、一定のチップ寸法モデル目標を達成すことが出来るようになった。世代内チップ寸法シュリンクモデルは、セル・ファクタ縮小の中間でのテクノロジ・ノードごとに  $0.5 \times$ である。

§§ MPU チップ寸法モデル: コスト重視 MPU と高性能 MPU の世代間チップ寸法成長率は、2018 年まで一定とされている  $(280 \text{mm}^2/ \text{コスト 重視 MPU 導入時; <math>140 \text{mm}^2/ \text{コスト}$  重視 MPU 量産時;  $310 \text{mm}^2/ \text{ 高性能 MPU}$  量産時)。この MPUのチップ寸法一定モデルは、テクノロジ・ノード・サイクルごとのオンチップ機能の倍増により可能となる。世代内チップ寸法シュリンクモデルは、2001 年まで 2 年テクノロジ・ノードごとに  $0.5 \times$  であり、2003 年以降は 3 年テクノロジ・ノードごとに  $0.5 \times$  である。

用語 - 導入、生産、世代間、世代内については、用語集を参照すること。